芯片规模包装的主要推动力是对小型化的市场需求,特别是便携式电子产品。但是,不管该推动力有多大,新的技术总是需要时间获得接受,因为支持的基本设施需要开发。对CSP快速接受的三个最大障碍是成本、PCB技术和可制造性。本文简要描述一个用来调查研究可制造性的工程项目,它包括一个来自涉及这基本设施的各公司代表所组成的合作小组。对球栅阵列(BGA)包装的强烈接受建立了一个先例,在这个先例上面,该合作小组设计和制造了用来探讨将CSP技术溶合到制造中去的试验载体。由于成本和电路板技术都与真实的试验载体的设计有关,所以也作简要的讨论。

CSP 技术趋势

集成电路(IC)包装的功能是提供芯片上的接合片与PCB上的通孔或者附着焊盘的空间转化。在通孔(through-hole)包装的时代,外包装引脚的间距通常是 100-mils(2.54mm)。表面贴装技术将周围引脚型包装的引脚间距推到 0.5 mm,现在是 0.4 mm。通过减少引脚间距到 0.3mm 来将包装密度提得更高,已经遇到了严重的阻力。用BGA技术,将周围引脚包装转换成面积排列,它提供豁然放松间距的一个新的替代方法。

在过去二十到三十年里发展的各种包装中,揭示了一个不变的趋势:包装越来越难达到其空间转化的功能。我们可以进行一个比较,一边是使用双排引脚框,从芯片到板上大量的输出端数;另一边是采用塑料球栅阵列(PBGA)包装,基板上高密度的布线。

CSP的出现带来甚至更大的困难。前面的包装提供从芯片模到外引脚的输出端数。可是,对于一个与芯片模相同尺寸的CSP,不存在包装内输出端的机会;相反,从接合焊盘到外部连接的输入端是必要的。甚至对一个比芯片模尺寸稍大的CSP,输出端可用的空间也十分有限。因此,多数CSP是通过非传统的方法,如柔性电路,构造的,因为引脚框和印刷电路基板是不能达到所要求的高布线密度。虽然包装内部的布线问题可通过构造方法解决,包装外的布线问题还是存在。

CSP的障碍

PCB技术  CSP的基本问题是硅技术进步比PCB技术更快。所有外部引脚不得不限制在芯片模的外形内或者裸露外面。随着硅处理技术的相继产生,芯片模缩小,外部引脚不可避免地缩小到超出传统的FR-4的布线能力。

CSP的基本问题是硅技术进步比PCB技术更快。所有外部引脚不得不限制在芯片模的外形内或者裸露外面。随着硅处理技术的相继产生,芯片模缩小,外部引脚不可避免地缩小到超出传统的FR-4的布线能力。

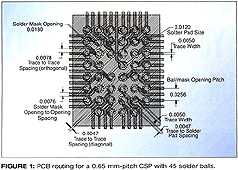

图一是为一个45个锡球在0.65mm间距上排列的CSP的电路板布线,显示它可以用合理的标准FR-4设计规则在一层上布线。可是,如果该CSP的间距由0.65mm减少到0.5mm,那么需要更进取的设计规则。在相同的0.65mm间距上为更高引脚数的包装布线也是昂贵的,因为有必要使用不只一个布线层、可能用到盲孔(blind via)因此,今天对CSP的需求多数局限在低引脚数的元件,如内存,间距范围是0.65mm~0.80mm。四周引脚的CSP可达到0.5mm的间距,可是,这些本来就局限于低引脚数。

当然,CSP的布线问题不是传统的FR-4的相对粗糙的设计规则所出现的唯一问题。小型化要求更细的线与空隔和更小的通路孔(via),简单地减少电路板“不动产”。因此,PCB工业正投入大量资金在有组合层和微型通路孔(microvia)的先进电路板技术,特别是在日本。随着具有先进电路板技术的产品变得越来越盛行,它们将使更复杂的CSP进入使用。可是,FR-4仍保持现在的标准,由于其低成本。

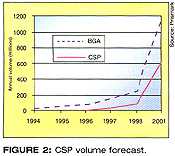

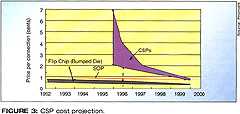

成本 图二显示一个世界范围内CSP产量的预告。今天的产量 - 在总IC量的大约0.05% - 很低。对接受CSP的另一个障碍是成本。CSP的现时成本非常高,通常比相当的传统包装贵 1.5 ~ 2 倍。随着产量增加,成本将可能接近传统包装的类似水平。多数CSP具有固有的低成本结构,应该最终匹敌那些基于引脚框的包装,如TSOP(thin small outline package)。图三显示未来成本的一个预测。

图二显示一个世界范围内CSP产量的预告。今天的产量 - 在总IC量的大约0.05% - 很低。对接受CSP的另一个障碍是成本。CSP的现时成本非常高,通常比相当的传统包装贵 1.5 ~ 2 倍。随着产量增加,成本将可能接近传统包装的类似水平。多数CSP具有固有的低成本结构,应该最终匹敌那些基于引脚框的包装,如TSOP(thin small outline package)。图三显示未来成本的一个预测。

将影响成本降低速度的因素是在研究开发和设备中的初始投资的回报有多快。产量达到形成规模效应的那一点的速度有多快,也将影响成本。

可制造性 第三个主要障碍是板的装配工艺。评估技术成熟性和开发基础设施的一个有效方法是通过一个在“食物链”中涉及关键角色的工作合作伙伴。为了调查研究CSP的准备状态,成立了一个合作小组:AMD公司提供硅与包装、Hadco和Zycon公司(在该工程项目期间是两间分开的公司)提供板、Solectron公司提供板的设计和装配技术、还有Tessera公司提供包装技术(µBGA™)。

第三个主要障碍是板的装配工艺。评估技术成熟性和开发基础设施的一个有效方法是通过一个在“食物链”中涉及关键角色的工作合作伙伴。为了调查研究CSP的准备状态,成立了一个合作小组:AMD公司提供硅与包装、Hadco和Zycon公司(在该工程项目期间是两间分开的公司)提供板、Solectron公司提供板的设计和装配技术、还有Tessera公司提供包装技术(µBGA™)。

到现在为止,传统的BGA已经在工业中得到“临界质量(critical mass)”的接受,由于易于电路板装配而得到加速。其焊接附着的最具戏剧性的方面是在回流期间锡球的自我对中(self-centering)。因为微型BGA也有一个阵列的锡球,它也会分享这个有利的特性。另一方面,锡球较小(0.3mm和大约0.65mm比较),间距更细小(0.5mm ~ 0.75mm 与1.0mm ~ 1.27mm比较)。合作小组的目标是要建立这些特性的最终结果。

电路板装配评估与试验载体设计

今天对CSP的应用都可能是诸如内存这样的低引脚数的元件和诸如微处理器之类的中等引脚数的元件(达到大约200)。因此,合作小组课题的一个目标是评估这些包装的可制造性,特别是一种设计用于闪存的44引脚的微型BGA,和一种188个输入输出的试验包装。内存所采用的两种间距是 0.65mm 和 0.75mm,两种都得到评估。那个188-I/O的试验包装是0.5 mm 间距的。

CSP应用大多数都可能包括各种其它的包装。为了探讨在制造合格率和为制造而设计设计(DFM, design for manufacturing)方面的问题,一个试验载体应该包括各种元件的混合和应该是双面的。表一列出了可选择的元件。

| ||||||||||||||||||||||||||||||||||||

电路板是传统的FR-4,与大多数今天便携式产品一致。包括该0.5mm间距的、188引脚的微型BGA包装的基本原因 - 虽然用传统的FR-4很难布线 - 是要评估是否电路板装配工艺可以就这样延伸应用到该包装,因此表示未来发展已经就绪。所有元件都是用串级链式的结构内部接合的,符合电路板上的串级链布局。因此,检查每个焊接点的电气连续性成为可能。板是用两种表面处理制造的:有机焊锡保护层(OSP, organic solder protectant)和镍/金涂层;HASL是不适合于这些密间距(fine pitch)元件的。

装配工艺过程

锡膏丝印工艺

与任何密间距装配一样,最大的关注放在锡膏的丝印过程。设计了一个试验来测试不同模板(stencil)开孔、模板表面光洁度和锡膏类型的影响。研究了两种锡膏,都是免洗的,生产中用于其它密间距元件。印好的锡膏经过视觉检查印刷品质,并用X光频谱分析来测量锡膏的量。结果显示唯一有重要影响的变量是模板开孔。使用最佳的开孔,两种锡膏类型都给出同样好的印刷品质。

装配了44-I/O微型BGA(0.75mm和0.65mm间距)每个版本的各一百块电路板。

焊接点品质的评估

焊接点品质的评估是通过视觉检查、X光和金相截面来进行的。另外,因为所有元件都是成串级链的,电气连续性可以100%进行。发现了两个锡桥缺陷,是误操作所引起的。换句话说,所有芯片规模与传统包装的焊锡点品质都是很好的,良好的熔湿与圆角。相当焊锡点的总数,两个缺陷就是每百万中12个元件(ppm, parts per milliom)。

焊接点可靠性评估 课题的最后阶段就是焊接点长期可靠性的评估。这个阶段的测试载体类似于可制造性试验载体,除了包括了CSP的另一个版本。这个版本将是一个密间距BGA(FBGA),也是设计用于闪存,但不同于微型BGA包装,因为锡球间距是0.8mm,并且FBGA缺少顺应层。

课题的最后阶段就是焊接点长期可靠性的评估。这个阶段的测试载体类似于可制造性试验载体,除了包括了CSP的另一个版本。这个版本将是一个密间距BGA(FBGA),也是设计用于闪存,但不同于微型BGA包装,因为锡球间距是0.8mm,并且FBGA缺少顺应层。

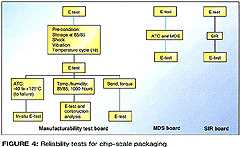

由于在相同的板上与其它元件一样有FBGA包装,那么在三种闪存包装之间 - 微型BGA、FBGA和TSOP - 以及在188引脚的微型BGA和100引脚的TQFP(tape quad flat pack)之间可以进行有趣的比较。试验的完整矩阵如图四所示。

设计预老化(preconditioning)来模拟在产品运输期间将发生的温度循环和振动。应力测试是相当标准的;值得特别一提的是表面绝缘电阻(SIR, surface insulation resistance) - 就是专门关注由于CSP的相对小的离地高度所引起的污物的夹藏 - 和机械偏转系统(MDS, mechanical deflection system),如果可以显示良好的相关性,那么它就是温度循环的快速替代方法。推测起来,多数兴趣将集中在ATC上面,它将提供焊接疲劳缺陷敏感性的数量上的测量。微型BGA有顺应层,可能产生最好的结果。

结论

一个制造过程已经证明可用于与现有的表面贴装工艺兼容的微型BGA包装,可以在同一块板上处理传统的表面贴装包装。和任何密间距技术一样,使用者应该特别注意优化锡膏印刷品质,这个可用现有的材料和传统模板完成。以该课题,获得好结果是简单的,得到12ppm的合格率。焊接点品质用各种测试来证实,所有三种CSP间距:0.5mm、0.65mm和0.75mm,都得到好的结果。

得到焊接点的好品质,可靠性结果也应该是好的,虽然不同包装类型表现不一样。可靠性试验结果应该可以转化成在产品的最终使用环境中得到的结果。不同的包装将适合于不同的要求。受可靠性测试结果的影响,在产品设计中包含CSP还没有被证实。

限制CSP技术向高引脚数和小于0.65mm间距扩展的另一个现实障碍是电路板技术的能力。传统的FR-4对于间距小至0.65mm的低引脚数元件是足够的。可是,除此之外,要求某种较高密度电路板技术,使用叠层和微型通路孔工艺。假设便携式电子产品制造商继续推动小型化和增加功能,那么即使没有CSP也会要求这种电路板技术。因此,主要的制造商希望引入各种使用高密度电路板的产品,提供接受更密间距CSP的适当平台。

传统的BGA已经在市场上得到迅速的接受,因为它们在电路板装配中达到很好的制造合适率。本课题已经用CSP取得类似的成功,因此我们得到一个期望:也许CSP可以比BGA更迅速地使用。

Acknowledgements

The authors wish to acknowledge: Ed Fontecha, AMD; Dr. Shelgon Yee and Harjinder Ladhar, Solectron; Elliott Pflughaupt, Tessera; and Robyn Aagesen, David Hoover, Greg Lucas and Jeff Dedow, Hadco-Zycan.

Dr. Srinivas Rao is vice president, technology - Solectron Corporation, Milpitas, CA; Srinivas-Rao@CA.slr.com. John Hunter is with AMD Inc., Sunnyvale, CA; (408) 732-2400. Contact the authors for more information about the project and its results.

沪公网安备 31011502005504号

沪公网安备 31011502005504号