板面焊接点可靠性信息的获得对于芯片规模包装(CSP, chip-scale backage)的广泛实施是关键的。本文比较三个不同的CSP概念及其装配的可靠性。另外,将使用一个修饰的Coffin-Manson关系,对一个专门的温度循环范围,设计出有关几种低输入/输出(I/O)包装的焊接点可靠性的循环数据文献。由喷气推进实验室(JPL, Jet Propulsion Laboratory, Pasadena, CA)组织了一个微型BGA协会,来探讨有关包装类型、I/O数、PWB材料与类型和制造变量对品质和电路板可靠性的相互作用的技术问题。这里呈现给大家的是来自这个课题的最新结果。

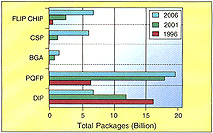

小型化的趋势 通孔(through-hole)和表面贴装(surface-mount)集成电路(IC)包装的预计用量根据市场的来源有很大的不同。来自BPA, UK的一项计划如图一所示。几个趋势是明显的。

通孔(through-hole)和表面贴装(surface-mount)集成电路(IC)包装的预计用量根据市场的来源有很大的不同。来自BPA, UK的一项计划如图一所示。几个趋势是明显的。

双排引脚包装(DIP, dual in-line package)预计用量上减少最多,从1996年的160亿在十年内减少到大约50亿,或者每年减少10亿。相反,表面贴装包装的用量,包括PQFP (plastic quad flat pack),预计在下一个十年内会增加。预计在五年内增加70~180亿,并且在另外的五年内几乎是稳定水平,只增加20亿。在十年内,COB(chip on board)预计从50亿增加到130亿,图一中未显示出。

CSP和倒装芯片(flip-chip)包装的用量上的增加是相同的。预计在2006年达到60亿。相反,在相同十年里BGA的增加预计是最小的,达到只有15亿的总用量。对BGA的预计表明也许这些包装只是一个踏步石,工业将更广泛地接受倒装芯片(flip chip)和芯片规模包装(CSP),因为它们更好地满足小型化应用的要求。

为什么采用芯片规模包装(CSP)?

为什么采用芯片规模包装(CSP)?

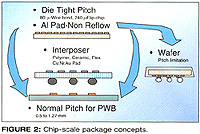

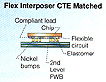

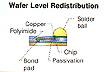

CSP的出现提供裸芯片(bare die)与倒装芯片(flip chip)的性能与小型的优势,具有标准芯片包装的优点。CSP设计成比芯片模(die)面积或周长大 1.2~1.5 倍的包装。图二说明CSP的两个概念,包括具有1)柔性或刚性内插器和2)圆片级(wafer-level)成型与装配再分布的两种包装。

- 包装达到如下的目的:

- 为回流焊接装配工艺提供与印刷线路板(PWB)焊盘冶金兼容的锡球和引脚。

- 重新把芯片模(die)紧密的间距分配成在PWB制造规范之内的间距水平。

- 由于小尺寸,不允许重大的重新分配;现在的低成本PWB制造限制了该技术的全面采用,特别是高输入输出(I/O)数。

- 防止芯片模的物理和阿尔发射线(alpha radiation)损坏,提供散热的载体。

- 使芯片模功能测试容易。

微型BGA的自我对中(Self-Alignment)

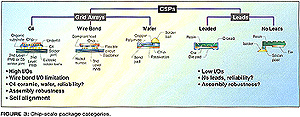

如图三所示,用输入输出(I/O)的可扩展性和制造的坚固性,CSP可分类成栅格阵列和引脚型(无引脚型)。列出了每个类型的主要优点/缺点。密间距(fine pitch)栅格阵列可接纳更高的引脚数,与BGA类似,它们具有自我对中特性。对BGA,包装贴装要求的放松已经广泛地认为与传统的表面贴装包装比较减少了焊接点的缺陷。

影响自我对中的主要因素是熔化的焊锡表面张力,它提供在包装上到焊盘的拉力。反作用力是包装的重量。对PBGA,从共晶锡球产生的拉力大于来自陶瓷BGA(CBGA)的部分熔化焊接点或者传统包装的锡膏熔化的力。因此,PBGA具有更好的自我对中。BGA锡球分布的对称性进一步允许对BGA的X和Y和旋转位移。

对于栅格式CSP,熔化的表面张力比BGA小得多,因为它们具有较低的锡球量。这个较小的表面张力,配合CSP较密的间距,可能阻碍自我对中表现,特别对于重的包装。CSP可能要求比50-mil间距的BGA更紧的贴装精度。

- 栅格CSP显示有自我对中,但是在最好的偏移限制上存在不和谐:

- 对于46个I/O的栅格CSP,只有25%的偏移是可接受的。可接受的偏移对于PBGA是62%,对于CBGA是50%。[Noreika, Surface Mount International(SMI), 1997]

- 另一个研究者报告一个80%的偏移。(Patridge, SMI 1997)

- 据说在16,100个焊接点中只有两个锡桥,是由于外来材料,没有来自贴装不准确的缺陷。该试验是一个定性研究,其中300个46 I/O的CSP是手放的,回流;然后刻画焊点缺陷(Bauer, et al, SMI 1997)。

- 在装配有44 I/O的CSP包装的200个装配中,只检查到两个焊接点短路(Hunter, at al, CHIPCON 1998)。

- 当JPL领导的微型BGA协会装配30个试验载体(每个载体都有四个46 I/O的CSP)时,没有观察到缺陷。

- 当八个具有160 I/O的CSP有0.2mm的偏移时,没有观察到缺陷。这个是针对0.45~0.23 mm直径的焊盘布局(IMAPS, 1997, p.256)。

微电子装配的可靠性

在包装附着中一个主要的损坏根源是改变系统温度。当系统没有使用时就关闭电源造成更多的循环。以前,电子硬件通常长期地保持有点,其结果是相对少的温度循环,引起对由温度循环影响的焊接点的关注。对焊接点的损坏最通常是由下面因素引起的:

- 包装与板之间总的温度膨胀系数(CTE, coefficient of thermal expansion)不匹配,引起应力。包装和板也可能在厚度上和表面积上有温度梯度。

- 在元件与PWB焊锡附着之间的局部的CTE不匹配。

减少元件与PWB的CTE不匹配可减少循环损坏,但是理想的条件决定于元件、PWB和焊锡的温度条件。具有比元件的CTE稍微较高的、CTE经过修整的PWB材料可能是理想的,因为,通常,总的CTE不匹配占上风,有热源芯片模的元件比PWB较热。

还有其它方法用来减少对焊接点的损坏。底部充胶(underfill)的应用是一个常见的技术,广泛用于板上芯片的直接附着或者当包装的引脚不牢固时。其它不太传统的方法目的是要在包装内吸收芯片模(die)与板之间的CTE不匹配,或者外部地通过应力吸收机构,减少焊锡连接上的应力。这些方法可能引起它们本身独特的损坏,因为最脆弱的连接现在从焊锡转移到附着系统的其它区域。

CSP装配的可靠性

表一分类了三个级别包装的装配可靠性。它包括对柔性或刚性内插件(interposer)的包装和圆片级包装(wafer-level)的可靠性试验数据。其失效机制的循环条件方面总结如下。

温度膨胀系数经过吸收的(CTE-absorbed)CSP

表一显示了对于一个CTE不匹配经过释放的包装的温度循环试验结果。该包装使用象IC内部连接一样的TAB(tape-automated-bond),一个有弹性的内连器和共晶锡球。这个与TAB内连接的弹性关联的有弹性的内连器减少芯片[CTE 2~3 ppm (parts per million)/°C]与PWB[FR-4的CTE 4~15 ppm/°C]之间的温度膨胀差别。这种包装已经显示其可靠性和稳固性,无需底部充胶。在表一中的温度循环/冲击是针对FR-4上的链型包装,是从液态氮温度(-196°C)到热油(160°C)温度范围内进行的。

由于焊接点的低应力状态,没有观察到焊接点的疲劳失效机制,失效转移到具有高不匹配应力水平的TAB内连接的脚跟部分。当使用柔软的金引脚时,发现有重要的改善。在-65°C~150°C范围内循环高达2,000次,金质的没有显示失效。与在极度低温与高温下装配暴露有关的温度循环屏蔽试验结果是不现实的,因此,它们的失效机制可能对现场失效(field failure)不具代表性。

由于极度高温暴露,一个这种失效是接近玻璃态转化温度(Tg),或者聚合材料开始变软的温度时, FR-4 的扩孔和变形。如果温度变得接近或超过Tg,那么PWB材料显示严重的损坏。在-65°C到150°C温度循环范围内,FR-4 电镀通孔(through-hole)发现有大量的内孔爆裂失效。

表一也包括来自两个用户的最新结果。失效的循环数比这个包装的供应商提供的少得多。来自英特尔(Intel)1997年底发表的数据也显示这个包装失效的循环数比来自摩托罗拉1998年五月发表的较高。前一个研究者被认为是有一个受控的元件包装供应商,而后者的包装来自不同的品排。

极度的CTE不匹配

对一个圆片重新分配(wafer-redistributed)包装的装配的温度循环试验结果在表一中显示。在这个包装中,一个薄片金属/聚合物重新分配锡球在芯片上的位置,以保证这些与表面贴装脚印兼容。这个包装类型的高度因为从裸芯片的金属聚合层厚度而增加。这个增加的层通常将不吸收芯片与板之间的CTE不匹配,因此,这个包装的装配可靠性预计与受控塌落芯片连接(C4, controlled collapse chip connection)装配很相似。

没有底部充胶材料,装配好的包装在受到0~100°C之间的温度循环时达不到40个循环就失效。对于这些包装类型,底部充胶通常要求达到装配可靠性的可接受水平。经过底部充胶的装配循环达到2,000次都不会失效。

刚性内连器的陶瓷包装

非圆片级的陶瓷包装在没有底部充胶时仍显示合理的装配可靠性。表一包括在FR-4上的一个陶瓷包装的温度循环结果。陶瓷CSP使用多层陶瓷(MLC, multilayer ceramic)一样的设计规则,温度压缩和金接线球的一级内连接选择,焊接倒装芯片和引线接合。强度、刚性、共面性和包装的容室是很好的。在一个0.6mm、低Tg温度的FR-4上的包装装配在-40°C~125°C之间大约600个温度循环失效。较厚的FR-4预计在暴露到125°C时显示较好的刚性,对本研究使用了接近低Tg的FR-4聚合体的温度。

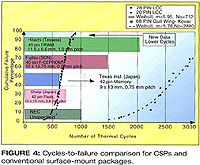

表面贴装,预计CSP可靠性 在JPL已经研究了传统表面贴装包装的可靠性。28与20脚的引脚芯片载体(LCC, leaded chip carrier)和68脚翅型(gull wing)装配的循环失效试验数据点及其Weibull分布在图四中显示。为了比较,也包括了低引脚数的CSP的预计失效循环次数。

在JPL已经研究了传统表面贴装包装的可靠性。28与20脚的引脚芯片载体(LCC, leaded chip carrier)和68脚翅型(gull wing)装配的循环失效试验数据点及其Weibull分布在图四中显示。为了比较,也包括了低引脚数的CSP的预计失效循环次数。

图四包括来种图表:LCC与翅型的分布图和CSP的单数据点。对于分布图,选择从Y轴的累积百分比(例如,50%),然后从X轴找到失效的循环数(例如,对20脚的LCC大约700次循环)。对于CSP,Y轴没有值,条的高度代表失效的循环数,其值由X轴定义。例如,Hitachi(Tessera)40 DRAM装配数据在-55~100°C循环可达将近2000次。可是,由其它公布的新数据显示对于来自不同供应商的包装的循环次数低得多,在该条的顶部上的箭头所显示。

对于LCC,从-55°C~100°C的温度循环有246分钟的持续时间。失效分布百分比是使用一个中间值绘图位置来近似表示,Fi = (i-0.3)/(n+0.4)。双参数Weibull累积失效分布用来配合该数据。

对于CSP,结果是那些从文献收集和从修整的Coffin-Manson关系预计的。多数CSP包装的板的可靠性是可比较的或者比其相应的LCC更好。可是,这些包装不象引脚包装(包括翅型和J型引脚)那么稳固。J型引脚的数据在图四中没有显示,因为达到3000次循环都没有焊接点失效发生。

系统地评估可靠性

板的可靠性信息对高可靠性应用的CSP实施是必要的。为了帮助在这些领域建造基础设施,JPL已经成立一个协会,目的是探讨有关包装类型、I/O数、PWB材料、表面光洁度和制造参数对装配包装品质与可靠性的相互作用的许多技术问题。

该课题的目标是展示CSP内连接的控制、品质和可靠性,支持一个产品保证与检查方法开发的,特别是装配级的,工业基础设施的发展。目标包括:

- 最佳包装类型构造的特征化

- 包装类型、I/O与环境依靠的可靠性特征化

- 返工技术

试验设计方法(DOE, design of experiment)用来改进效率。切换的变量包括:包装的I/O与构造、PWB材料、制造工艺过程和环境条件。检查技术用来决定环境暴露期间损坏的进展。失效循环数据使用Weibull失效分布和预计寿命的Coffin-Manson关系来分析。

CSP实施的挑战

有关CSP技术实施的各个方面所标记的挑战可作如下总结:

成熟性和有效性

使用与附着可靠性评估的CSP的有效性是最具挑战性的问题。对大范围的CSP有许多的论文存在,但是多数包装是在其发展的早期阶段,缺少包装可靠性数据。多数包装只有原型的形式,但是不包装统一的包装特征或可有生产版本的形式存在。包装发货比预计时间拖延是正常的事。

缺少设计指引标准

现在,没有CSP各元素的指引和标准。对于我们的设计,当可得到时,就使用包装供应商开发的指引。否则,只考虑现有的知识和工程判断。所选择的包装具有不同的间距、锡球量、锡球成分和链式布局。在多数情况中,这些布局是无规律的,设计需要许多时间和努力,这对具有较高I/O和许多链式曲径的包装尤其麻烦。

PWB材料

标准的PWB设计可用于低I/O的CSP。试验载体包括了几个这类包装,目的是当使用传统的PWB设计时确认装配的可靠性。较高I/O的有源芯片包装要求使用集结式(微型通路孔microvia)电路板技术。可是,为了测试的目的,在标准板上设计高I/O链式包装的可能的。试验载体的另一个形式包括具有微型通路孔技术的PWB。

应用

选择了许多I/O从低到高的包装描述特征。在今后一到三年内,主要的包装将是那些少于50 I/O的,虽然特殊的应用要求可利用I/O高得多的包装。预计另一个设计与装配的挑战是在一块板上混合有传统表面贴装包装、直接芯片附着、BGA和CSP。

试验载体设计

该协会同意集中在CSP技术的以下几个方面:

包装

选择了从引脚与无引脚的到微型BGA的许多包装来作评估。I/O数的范围从12到540,以满足短期与长期的应用。

PWB材料与制造

有树脂覆铜形式的FR-4和BT(bismaleimide trazine)两种材料用来评估。使用了标准板和微型通路孔板两种技术。在链式设计中,标准PWB技术不能用于大多数的包装。

表面最后涂层

至少有三种将考虑用作评估:有机焊锡保护剂(OSP, organic solder protectant)、热空气焊锡均衡法(HASL, hot air solder leveling)和金/镍涂层。三种锡膏将要评估:免洗(no-clean) 、水溶性(water soluble)和温柔激化的树脂(RMA, rosin mildly activated)。

底部充胶(underfill)

有底部充胶要求的包装将在有和没有充胶的情况下评估,以更好地理解不使用充胶的可靠性结果。

试验载体特征

试验载体是4.5"x4.5",并且分成四个独立的区。每个区有四个菊花链,可以在不影响其它区的菊花链的情况下切割作失效分析。

环境测试

为了将我们的数据与那些为BGA产生的联系起来,将考虑这些条件:-30~100°C 和-55~125°C。还有,温度循环将在0~100°C之间完成。将进行机械振动与冲击,理论模型将按需要建立。

微型BGA课题的现状

该协会已经完成了两个试验载体的设计:一个来自集体小组的努力(TV-1),另一个由一个小组成员开始的(TV-H)。TV-H的试验装配现在完成。这些装配现在正在评估,以决定在生产之前是否要求改变。剩下唯一的挑战是对一个倒装片包装的工艺优化。发现了有锡桥和没有锡桥的倒装片。锡桥的一个可能的原因是焊盘之间缺少阻焊层,由于密间距形式而无法使用阻焊层。

TV-1试验板用来优化装配过程和确认菊花链(daisy chain)的连续性。该协会现在正使用来自9个供应商的16个包装来装配试验板。I/O数从12到540。完全生产将在试验载体确认符合设计之后进行。

结论

自我对中,它使元件包装容易贴装到板上,是栅格式CSP比较引脚型最主要的特性。还没有建立得到可接受焊接点的贴装偏移水平。对CSP可能要求比BGA更紧的贴装控制。

CSP装配的可靠性决定于包装类型和对圆片级最低值、陶瓷的中等值和CTE吸收类型的最高值。底部充胶对圆片级包装是要求的,它也可用来提高大多数其它包装的可靠性。

对几种低 I/O 的CSP,焊接点的预计失效的温度循环次数比在JPL完成的表面贴装引脚型包装的试验结果低。这些包装比低I/O无引脚包装具有可比较的或者更好的可靠性。

传统上,焊接点失效已经被认为是微电子装配可靠性中的最薄弱的连接,但这对具有创新设计的CSP可能不是真的。基于焊接点失效由一个制造模型的人所作的预计比试验的测试结果高一个数量级。

在一些情况中,循环温度范围可能严重,引起不代表现场应用的失效机制。需要更深入的试验与失效分析来建立装配可靠性结果的信心。

JPL领导的协会的形成是要系统地探讨CSP装配的可靠性。理解满足系统要求的试验的全部哲理,发现与CSP相联系的新的失效机制,是收集有意的试验结果和建立这个技术的基础设施的关键。

Acknowledgements

The Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration (NASA), is performing this research. The author would like to acknowledge in-kind contribution and cooperative efforts of the microBGA consortium team members and those who have contributed to the progress of this program.

Dr. Reza Ghaffarian is senior engineer, applications engineering group - Jet Propulsion Laboratory, California Institute of Technology, Pasadena, CA; (818) 354-2059; e-mail: Reza.Ghaffarian@JPL.NASA.Gov.

沪公网安备 31011502005504号

沪公网安备 31011502005504号